Nvidia芯片工艺洞察和推演

上篇“Nvidia AI芯片路线图分析与解读”。

半导体工艺演进洞察

根据IRDS的乐观预测,未来5年,逻辑器件的制造工艺仍将快速演进,2025年会初步实现Logic器件的3D集成。TSMC和Samsung将在2025年左右开始量产基于GAA (MBCFET)的2nm和3nm制程的产品 [17]。

按照TSMC给出的工艺演进路标,2023~2025年基本以3nm工艺为主,2nm工艺在2025年以后才会发布。3nm技术已经进入量产阶段,N3工艺和N3E版本已经于2023年推出。2024年下半年开始生产N3P版本,该版本将提供比N3E更高的速度、更低的功耗和更高的芯片密度。此外,N3X版本将专注于高性能计算应用,提供更高的时钟频率和性能,预计将于2025年开始量产 [18]。工艺演进的收益对于逻辑器件的收益小于50%,因此,未来单芯片算力提升将更依赖于先进封装技术。

先进封装演进洞察

TSMC的CoWoS先进封装工艺封装基板的尺寸在2023年为4倍Reticle面积,2025年将达到6倍Reticle面积 [19]。当前Nvidia H100 GPU的封装基板尺寸小于2倍Reticle面积,AMD的MI300系列GPU的封装基板尺寸大约为3.5倍Reticle面积,逼近当前TSMC CoWoS-L工艺的极限。

HBM内存演进洞察

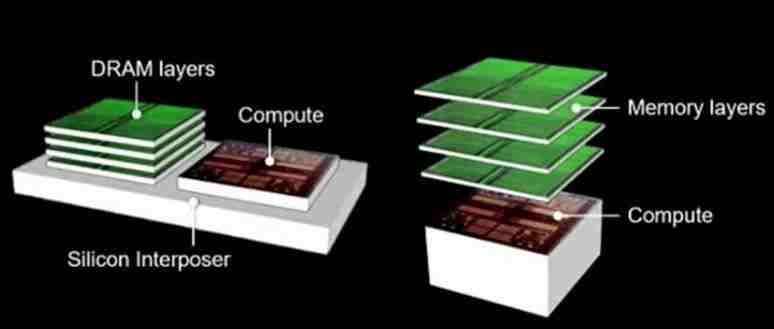

HBM内存的容量预计将在2024年达到24GB,并在2025年进一步增长至36GB [20]。HBM4预计将带来两个重要的变化:首先,HBM接口位宽将从1024扩展到2048;其次,业界正在尝试将HBM内存Die直接堆叠在逻辑Die的上方 [21][22]。这两个变化意味着HBM内存的带宽和单个封装内能容纳的容量都将持续增长。

据报道,SK海力士已经开始招聘CPU和GPU等逻辑半导体的设计人员。该公司显然正在考虑将HBM4直接堆叠在处理器上,这不仅会改变逻辑和存储器设备的传统互连方式,还会改变它们的制造方式。事实上,如果SK海力士成功实现这一目标,这可能会彻底改变芯片代工行业 [21][22]。

推演假设

本文基于两个前提假设来推演Nvidia未来AI芯片的架构演进。首先,每一代AI芯片的存储、计算和互联比例保持大致一致,且比上一代提升1.5到2倍以上;其次,工程工艺演进是渐进且可预测的,不存在跳变,至少在2025年之前不会发生跳变。到2025年,工艺将保持在3nm水平,但工艺演进给逻辑器件带来的收益预计不会超过50%。同时,先进封装技术预计将在2025年达到6倍 Reticle面积的水平。此外,HBM内存容量也将继续增长,预计在2024年将达到24GB,而在2025年将达到36GB。

作者:陆玉春

来源:

https://www.chaspark.com/#/hotspots/950120945305616384

更多GPU技术细节,请参考文章“最新版:GPU显卡天梯图(2023年11月)”,“全球GPU呈现“一超一强”竞争格局”,“2023年GPU显卡词条报告”,“HBM崛起:从GPU到CPU”,“英伟达GPU龙头稳固,国内逐步追赶(2023)”,“英伟达L40S GPU架构及A100、H100对比”,“AI芯片第一极:GPU性能、技术全面分析”,“主流国产GPU产品及规格概述(2023)”,“新型GPU云桌面发展白皮书”,“国内外GPU现状:海外龙头领跑,国产差距明显”,“GPGPU流式多处理器架构及原理”等等。

相关阅读:

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

全店内容持续更新,现下单“架构师技术全店资料打包汇总(全)”一起发送“服务器基础知识全解(终极版)”和“存储系统基础知识全解(终极版)”pdf及ppt版本,后续可享全店内容更新“免费”赠阅,价格仅收249元(原总价399元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“架构师技术全店资料打包汇总(全)”电子书资料详情。

最新评论

推荐文章

作者最新文章

你可能感兴趣的文章

Copyright Disclaimer: The copyright of contents (including texts, images, videos and audios) posted above belong to the User who shared or the third-party website which the User shared from. If you found your copyright have been infringed, please send a DMCA takedown notice to [email protected]. For more detail of the source, please click on the button "Read Original Post" below. For other communications, please send to [email protected].

版权声明:以上内容为用户推荐收藏至CareerEngine平台,其内容(含文字、图片、视频、音频等)及知识版权均属用户或用户转发自的第三方网站,如涉嫌侵权,请通知[email protected]进行信息删除。如需查看信息来源,请点击“查看原文”。如需洽谈其它事宜,请联系[email protected]。

版权声明:以上内容为用户推荐收藏至CareerEngine平台,其内容(含文字、图片、视频、音频等)及知识版权均属用户或用户转发自的第三方网站,如涉嫌侵权,请通知[email protected]进行信息删除。如需查看信息来源,请点击“查看原文”。如需洽谈其它事宜,请联系[email protected]。